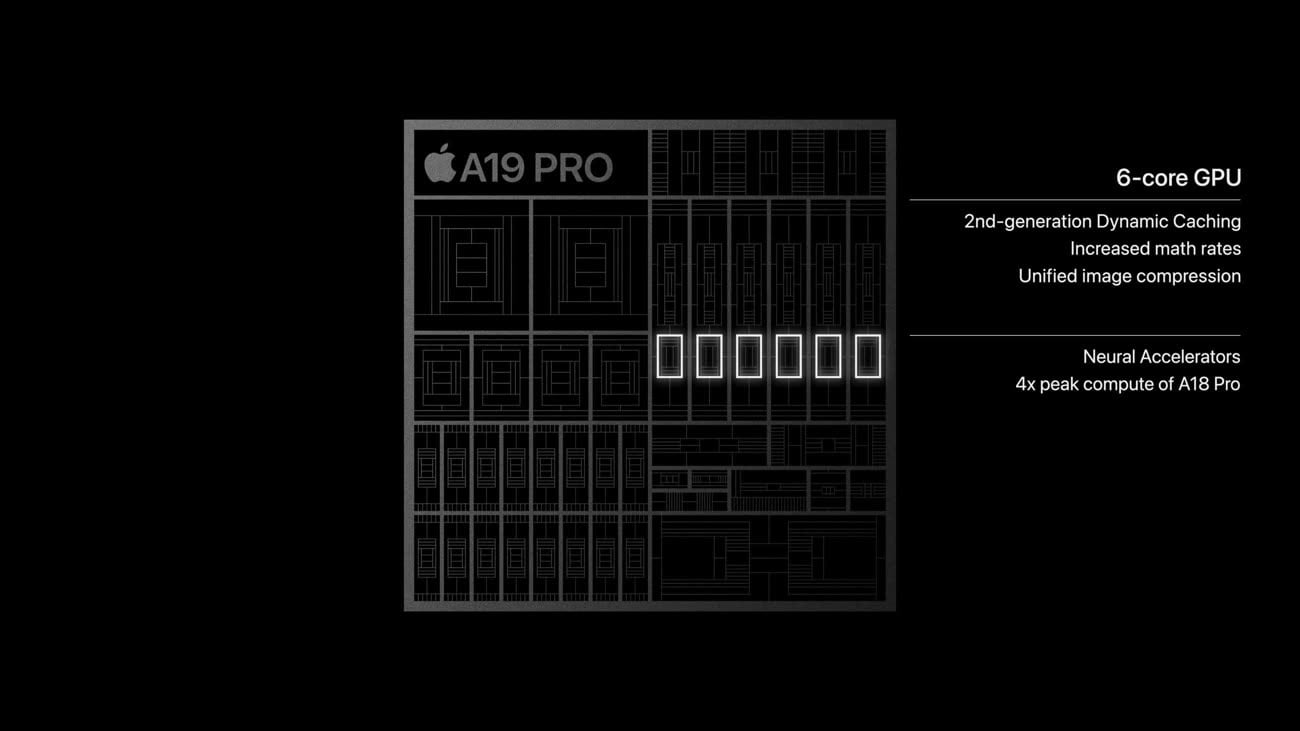

Une analyse de l'A19 Pro d'Apple montre des changements plus importants que prévu sur la gravure

Quand Apple sort une nouvelle puce, de nombreuses personnes se mettent à analyser l'intérieur du système sur puce, en tenant de deviner ce que cachent les transistors (et en démontant des iPhone pour décaper les puces à l'acide, aussi). Nous avons parlé d'une analyse de l'A19 de l'iPhone 17 peu après sa sortie, mais une image annotée de la structure de l'A19 Pro permet de mettre en avant des changements subtils mais efficaces chez Apple.

Une analyse en profondeur de l'A19 de l'iPhone 17

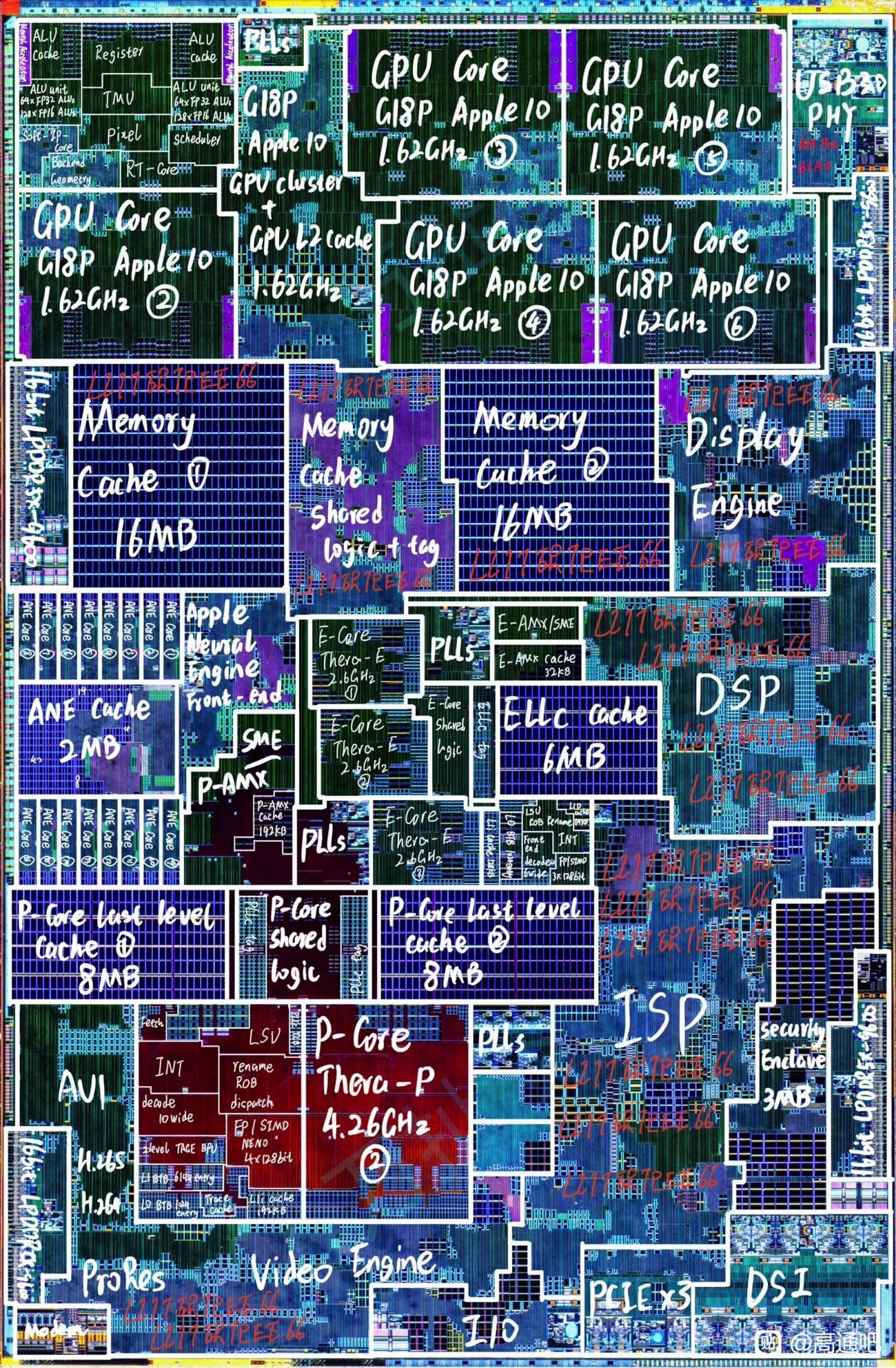

Le point intéressant noté par SemiAnalysis, c'est que la puce A19 Pro est environ 10 % plus compacte que l'A18 Pro, et que l'A19 est à peu près 9 % plus compact que l'A18. Pourtant, le passage de la gravure en 3 nm N3E de TSMC vers la gravure en 3 nm N3P (plus évoluée) ne doit permettre qu'un gain de 4 % environ selon le fondeur, et en partant du principe que les deux systèmes sur puce sont identiques, ce qui n'est pas le cas. Les puces A19 et A19 Pro sont en effet plus performantes et contiennent plus de transistors.

Selon eux, la raison est simple : Apple a optimisé ses composants de façon intelligente. Premièrement, les cœurs P (performants) sont un peu plus compacts (de l'ordre de 4 %) quand les cœurs E (basse consommation) et les cœurs de la partie graphique sont plus gros (d'environ 10 %). C'est un changement logique, compte tenu des performances : le gros des gains de la génération de 2025 vient justement des cœurs basse consommation et du GPU.

Mais ils expliquent surtout qu'Apple a optimisé certaines zones (le contrôleur pour l'affichage, les fonctions de sécurité, etc.) pour qu'elles nécessitent moins de transistors. Et en parallèle, la mémoire cache — qui représente une bonne partie de la surface — est passée sur une organisation qui permet de réduire le nombre de transistors à capacité identique. Selon eux, on passe de 1,08 mm2 pour 4 Mo dans l'A18 à 0,98 mm2 dans les A19.

Une réduction de la taille d'une puce est toujours un avantage technique évident, ne serait-ce que pour le rendement. La surface du wafer, la structure employée pour graver des puces, est fixe, comme son coût. Donc si la surface de la puce est réduite, il est possible d'en graver plus pour un coût identique, ce qui réduit le prix unitaire. De plus, en considérant que le taux d'erreur est constant, une puce plus petite implique mécaniquement un rendement plus élevé. Bien évidemment, ce sont des paramètres qui dépendent d'une chose : le prix du wafer. Et dans le cas de TSMC, la version en N3P est a priori plus onéreuse que celle en N3E.

Le chip binning, c'est bien plus que de vous vendre des puces défectueuses

Dans tous les cas, l'analyse montre qu'Apple ne se contente pas d'améliorer les performances de ses différents blocs ou d'ajouter de la mémoire cache, mais qu'il y a aussi une réelle réflexion pour mieux tirer parti des processus de gravure. Un choix qui n'est pas systématique chez tous les constructeurs : dans une itération qui consiste essentiellement à améliorer (un peu) les performances en profitant d'une gravure plus efficace, il est tentant de se contenter de garder une puce avec une taille physique identique en ajoutant de la mémoire cache. Apple, ici, a amélioré les performances et optimisé le tout pour produire une puce plus compacte, un choix rare.

La prochaine révision du moniteur Studio Display d'Apple intégrerait bien un écran compatible avec la technologie ProMotion, d'après une découverte de MacWorld dans une version interne d'iOS 26 à l'origine mystérieuse. Des portions de code évoqueraient en effet la prise en charge d'un taux...

La prochaine révision du moniteur Studio Display d'Apple intégrerait bien un écran compatible avec la technologie ProMotion, d'après une découverte de MacWorld dans une version interne d'iOS 26 à l'origine mystérieuse. Des portions de code évoqueraient en effet la prise en charge d'un taux...